iMX6系列应用笔记-iMX6Q GPIO 功能应用操作讲解

一、通用GPIO的使用

在嵌入式系统中对GPIO的操作是最基本的操作。在Linux中有一个通用的GPIO操作接口。在imx6Q开发板文件系统中会有一个控制GPIO的目录:/sys/class/gpio;Linux-3.0.35内核中Documention文件夹下边有gpio.txt文档可以参考。

root@freescale /sys/class/gpio$ ls export gpiochip0 gpiochip160 gpiochip32 gpiochip96 gpiochip128 gpiochip192 gpiochip64 unexport

| 名称 |

描述 |

|

export |

导出GPIO操作接口 |

|

unexport |

撤销GPIO操作接口的导出 |

|

gpiochip0 |

GPIO1组 |

|

gpiochip32 |

GPIO2组 |

|

gpiochip64 |

GPIO3组 |

|

gpiochip96 |

GPIO4组 |

|

gpiochip128 |

GPIO5组 |

|

gpiochip160 |

GPIO6组 |

|

gpiochip192 |

GPIO7组 |

其中,export和unexport为GPIO子系统的属性文件,其余七个文件则为符号链接(gpiochip0,gpiochip32,gpiochip64,gpiochip96,gpiochip128,gpiochip160,gpiochip192),分别指向各自对应的GPIO组。以gpiochip0为例,此目录下的文件有:

root@freescale /sys/class/gpio/gpiochip0$ ls base label ngpio power subsystem uevent

|

名称 |

描述 |

|

base |

GPIO组的初始编号 |

|

label |

GPIO组标签 |

|

ngpio |

该组的GPIO总数 |

|

power |

设备供电方面的相关信息 |

|

subsystem |

符号链接,指向父目录 |

|

uevent |

内核与udev(自动设备发现程序)之间的通信接口 |

当我们操作某个GPIO之前,需要先向export文件写入该GPIO编号以导出它的设备目录。GPIO编号的计算公式如下所示:

GPIO编号=(BANK-1)*32+N

在公式中BANK为GPIO引脚所在的GPIO组编号,N则为引脚在该个BANK中的序号。以GPIO7-IO03 为例,其BANK值为7,N值为3,因此排列序号为(7-1)*32+3=195。

下面介绍该目录下的一些操作的用法。

1、GPIO编号导出

文件系统中/sys/class/gpio/export文件用于通知系统需要导出要控制的GPIO的编号:echo 195 >/sys/class/gpio/export

命令成功后生成/sys/class/gpio/gpio195目录。如果没有出现相应的目录,说明此引脚不可导出,一般这种情况是驱动中pinmux功能配置不正确,或者配置了多种pinmux功能引起冲突导致。

2、取消GPIO编号导出

文件系统中/sys/class/gpio/unexport文件 用于通知系统取消GPIO编号导出:echo 195 > /sys/class/gpio/unexport

3、 配置GPIO的输入输出方向

echo out >/sys/class/gpio/gpio195/direction

direction可接收的参数:in,out,high,low;其中high,low设置方向为输出并将value值设置为相应的1/0。

4、查看GPIO的输入输出方向:cat /sys/class/gpio/gpio195/ direction

5、配置GPIO的高低电平(值为1/0)

当gpio配置为输出模式时,可以通过设置value值设置gpio的高低电平。

echo 1 >/sys/class/gpio/value

6、 查看GPIO的输出值cat /sys/class/gpio/gpio195/value

二、修改Pinmux配置

驱动中的主要位置:linux3.0.35/drivers/gpio/gpiolib.c

修改文件arch/arm/mach-mx6/board-mx6q_sabresd.h,在其中增加该引脚对应的gpio配置,该引脚如果有其他复用配置,需要将其他复用配置去掉,只保留一种pinmux配置。内核中引脚功能定义在arch/arm/plat-mxc/include/mach/iomux-mx6q.h文件中,该文件对每个引脚的复用功能进行了定义,有兴趣的可以自己看一下。

以释放原SD卡功能占用的部分引脚为例:

修改文件arch/arm/mach-mx6/board-mx6q_c_sabresd.h,在其中增加如下定义:

/*GPIO*/3

MX6Q_PAD_SD3_CLK__GPIO_7_3,

MX6Q_PAD_SD3_CMD__GPIO_7_2,

MX6Q_PAD_SD3_DAT2__GPIO_7_6,

MX6Q_PAD_SD3_DAT3__GPIO_7_7,

MX6Q_PAD_SD3_DAT4__GPIO_7_1,

MX6Q_PAD_SD3_DAT5__GPIO_7_0,

MX6Q_PAD_SD3_DAT6__GPIO_6_18,

MX6Q_PAD_SD3_DAT7__GPIO_6_17,

MX6Q_PAD_NANDF_D1__GPIO_2_1,

MX6Q_PAD_NANDF_D0__GPIO_2_0,

将原来的SD卡的功能注释掉

/* USDHC3 */

/* MX6Q_PAD_SD3_CLK__USDHC3_CLK_50MHZ,

MX6Q_PAD_SD3_CMD__USDHC3_CMD_50MHZ,

MX6Q_PAD_SD3_DAT0__USDHC3_DAT0_50MHZ,

MX6Q_PAD_SD3_DAT1__USDHC3_DAT1_50MHZ,

MX6Q_PAD_SD3_DAT2__USDHC3_DAT2_50MHZ,

MX6Q_PAD_SD3_DAT3__USDHC3_DAT3_50MHZ,

MX6Q_PAD_SD3_DAT4__USDHC3_DAT4_50MHZ,

MX6Q_PAD_SD3_DAT5__USDHC3_DAT5_50MHZ,

MX6Q_PAD_SD3_DAT6__USDHC3_DAT6_50MHZ,

MX6Q_PAD_SD3_DAT7__USDHC3_DAT7_50MHZ,

MX6Q_PAD_NANDF_D0__GPIO_2_0,

MX6Q_PAD_NANDF_D1__GPIO_2_1, */

修改前:

修改后:

修改完成后重新编译内核,并将镜像烧写到iMX6Q开发板上进行测试。

测试

echo 195 > /sys/class/gpio/export

echo out > /sys/class/gpio/gpio195/direction

echo 1 > /sys/class/gpio/gpio195/value

cat /sys/class/gpio/gpio195/value

三、Datasheet查看gpio

1、GPIO地址

IMX6DQRM.pdf手册中的第28章描述的是gpio相关的内容。

手册第二章Memory Maps内存映射大概在215页,有关于GPIO组的映射地址:

2、GPIO寄存器

数据手册第28章中第1429页描述的是GPIO控制的8个32位寄存器。

|

寄存器 |

描述 |

|

GPIOx_DR |

数据寄存器,当GPIO为输出时,可以通过写DR寄存器来驱动gpio引脚 |

|

GPIOx_GDIR |

控制GPIO引脚方向 |

|

GPIOx_PSR |

当GPIO为输入时,从PSR寄存器读取数据 |

|

GPIOx_ICR1 |

配置GPIO中断的触发方式,高低电平出发还是沿触发 |

|

GPIOx_ICR2 |

配置GPIO中断的触发方式,高低电平出发还是沿触发 |

|

GPIOx_IMR |

中断屏蔽寄存器 |

|

GPIOx_ISR |

中断状态寄存器 |

|

GPIOx_EDGR_SEL |

设置边沿触发方式 |

3、引脚复用

iMX6Q数据手册36章IOMUX Controller这一章节有兴趣的也可以详细看一下或者从网络上找一些相关资料了解,此处不做详述

该章节主要描述引脚的复用配置以及一些功能的配置等,内核代码中关于这一块的配置在linux-3.0.35/arch/arm/plat-mxc/include/mach/iomux-mx6q.h文件中。该文件中的具体配置有兴趣的可以自己看一下,一般这块恩智浦NXP官方是默认配置好的,配置项的具体含义也可以从网上搜搜,并结合iomux-mx6q.h文件自己看看。

4、参数查找配置方法

手册第四章查找EIM_A22,可以看到需要ALT Mode是ALT5,而且Pad Settings需要配置的参数有PKE – ENABLED, 对应的Pad Registers为[SW_PAD_CTL_PAD_EIM_ADDR22]。

手册继续搜索[SW_PAD_CTL_PAD_EIM_ADDR22] 寄存器, 可以看到寄存器的具体配置和具体的偏移地址以及上拉的配置。

手册寻找对应的MUX Control Registers [IOMUXC_SW_MUX_CTL_PAD_EIM_ADDR22]。可以看到具体的配置模式ALT5模式的配置值为0x05UL。

附录:常见GPIO调试问题处理参考

常见GPIO调试问题处理参考:

1.如果在GPIO导出时出现Device or resource busy的情况

一般都是该引脚在内核中配置为其他功能,需要仔细检查内核中引脚配置,不要被其他功能占用。

2.GPIO能够导出,但是使用的时候各种功能都不正常的情况

这种情况一般也是引脚在内核中配置为其他功能,需要仔细检查内核中引脚配置,不要被其他功能占用(一般被串口占用会有这种情况);

还有就是检查硬件电路,看硬件上有没有上拉下拉这样的硬件控制。

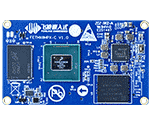

相关产品 >

-

FETMX6Q-C核心板

i.MX6Q核心板板层出不穷,要如何选择?飞凌解读i.mx6Q芯片强性能为您推荐四核A9架构的i.MX6Q产品精选,包含iMX6Q 核心板、i.MX6Q 核心板、iMX6Q工业级核心板,欢迎采购。 i.MX6Q核心板基于NXP(原Freescale)Cortex-A9架构的i.MX6Q四核处理器设计,核心板小尺寸核心板搭配独特的薄款连接器,让设计随心所欲!

了解详情

-

FETMX8MP-C核心板

iMX8MP核心板基于 NXP i.MX 8M Plus 处理器设计, 采用4核Cortex-A53 和 Cortex-M7架构。支持双千兆网口,iMX8MP性能强劲最高运行速率可达2.3TOPS,并且i.MX8MP功耗更低≤2W 。iMX 8M Plus系列专注于机器学习和视觉、高级多媒体以及具有高可靠性的工业自动化。它旨在满足智慧家庭、楼宇、城市和工业4.0应用的需求。飞凌iMX8MP核心板提供用户手册,iMX8MP原理图,引脚定义等。

了解详情